首个 2nm 制程芯片,竟然是 IBM 先发布的。

没错,不是已经研究出 3nm 技术的台积电,也不是已经量产 5nm 芯片的三星,而是 IBM。

据 IBM 官方表示,这种技术能在指甲盖大小(150mm?)的芯片上安装 500 亿个晶体管。

相比于 7nm 芯片,这种技术预计将提升 45% 的性能、并降低 75% 的能耗。

不过,这并不意味着 IBM 就具备量产 2nm 芯片的能力,因为这项技术是在它位于纽约州奥尔巴尼(Albany)的芯片制造研究中心做出来的,但量产还涉及许多其他技术。

由于 IBM 自己没有 10nm 制程以下的晶圆厂,因此要想这个 2nm 工艺实现量产,可能还需要找其他晶圆厂代工。

这么看来,距离我们真正用上 2nm 芯片,可能还需要几年的时间。

那么,2nm 芯片到底怎么做出来的?

IBM 的 2nm,什么技术?

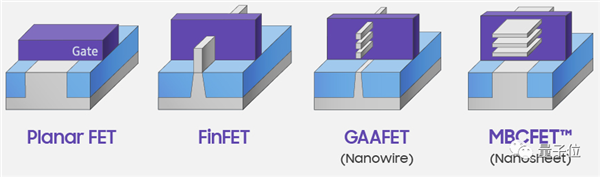

此前,业界普遍采用 FinFET (鳍式场效应晶体管)结构,但在 5nm 节点后,这种结构难以满足晶体管所需的静电控制,出现严重的漏电现象。

三星率先采用了名为 GAA(gate-all-around,环绕式栅极)的晶体管技术,对 3nm 制程芯片进行研发,IBM 的 2nm 制程所采用的技术,也同样是 GAA。

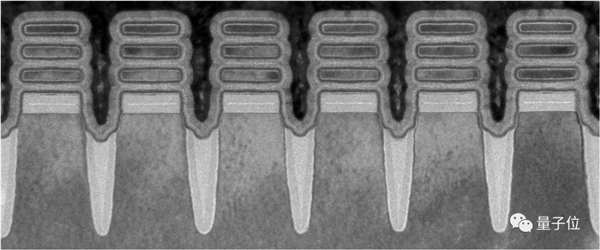

其中,GAA 分为纳米线结构(下图左三)和纳米片结构(下图右一,MBCFET 是三星商标)两种,这次 IBM 采用的就是纳米片结构。

相比于纳米线结构,纳米片结构的长宽比较高,接触面积更大,但也更难控制片与片之间的刻蚀与薄膜生长。

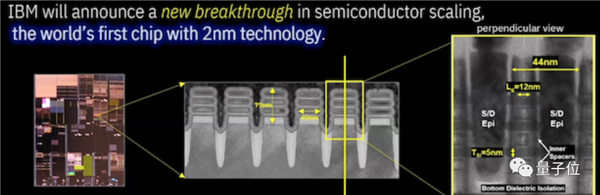

从图中可见,IBM 的 2nm 芯片中,纳米片共有三层,每片纳米片宽 40nm,高 5nm,间距 44nm,栅极长度 12nm。

嗯???

没错。这里 IBM 的 2nm 早已经不指栅极长度(MOS 管的最小沟道长度),而是等效成了芯片上的晶体管节点密度。

密度越大,芯片的性能就越高。至于 2nm,只是一个命名方式而已。

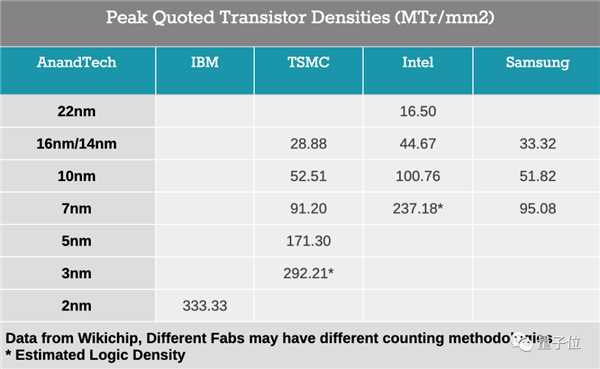

这个芯片的密度达到了 333MTr/mm?,即每平方毫米容纳 3.3 亿个晶体管。

作为对比,台积电的 5nm 芯片密度为 171.3MTr/mm²,三星的 5nm 芯片密度则为 127MTr/mm²。

除此之外,IBM 的 2nm 芯片,这次还采用了不少其他技术:

底部电介质隔离(bottom dielectric isolation),用于减少漏电、降低功耗

内层空间干燥处理(inner space dry process),用于精准门控

EUV 光刻技术,用于图案化薄膜或大部分晶片部件

对于这次研究的突破,IBM 混合云研究副总裁 Mukesh Khare 表示:

没什么障碍是我们不能突破的。随着技术成熟,还会有更多突破出现。相比于困难,我看到的反而是创新的动力和前进的机会。

不过,这并不意味着 2nm 芯片实现了量产。

实验室做出来≠量产

一个工艺从实验室出来,到大规模量产,过程中需要芯片代工厂不断提升晶圆良率。

晶圆良率,指完成所有工艺步骤后,测试合格的芯片的数量与整片晶圆上的有效芯片的比值。

因此,晶圆良率决定了芯片的工艺成本。

要是一个工艺的晶圆良率上不去,量产可能反而会导致芯片亏损。

而目前,IBM 的 2nm 芯片还停留在实验室阶段,只是制造出来而已。

除此之外,也还需要考虑光刻机等工具的进展。

比较有意思的是,IBM 现在是没有大规模量产芯片的能力的,更可能将这项工艺交给三星等芯片制造商代工(目前已与英特尔和三星签署联合开发协议)。

IBM 虽然曾经也是芯片制造商之一,却在 2014 年将自己的晶圆厂出售给了格罗方德(据说 IBM 还向格罗方德交了 15 亿美元,才把晶圆厂塞给它)。

那么,目前几家芯片厂商的进展具体如何呢?

从量产情况来看,台积电和三星均已实现了 5nm 量产。

而从制造工艺来看,IBM 直接实现了 2nm 的飞跃,台积电目前研发出 3nm 制程,预计今明两年实现量产。

三星目前也在研发 3nm 制程的芯片。至于英特尔,则还在 7nm 芯片上挣扎,量产预计要等到 2023 年。

不过,从图中也能看出,各厂商对于芯片的命名标准并不一致。

对于 IBM 的这次突破,市场分析公司 IDC 的研究主管 Peter Rudden 表示:

这可以被看成是一个突破,毕竟对于某些厂商来说,7nm 就已经是个巨大的挑战了。

同时,这也向 IT 行业传递了一个信号,即 IBM 仍然是一家硬件厂商巨头。

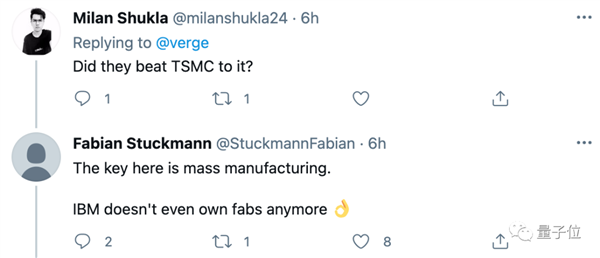

不过,也有网友表示,这并不意味着 IBM 的进程就超过了台积电:“关键在于大规模量产,然而,IBM 现在还没有自己的晶圆厂。”

让我们期待一波 2nm 制程芯片量产的消息。